一、芯片制造流程简介

1.1 硅片制备

- 原料提纯:从石英砂中提取高纯度硅,制成单晶硅棒并切割为晶圆片。

- 晶圆清洗:去除表面杂质,确保后续工艺的洁净度。

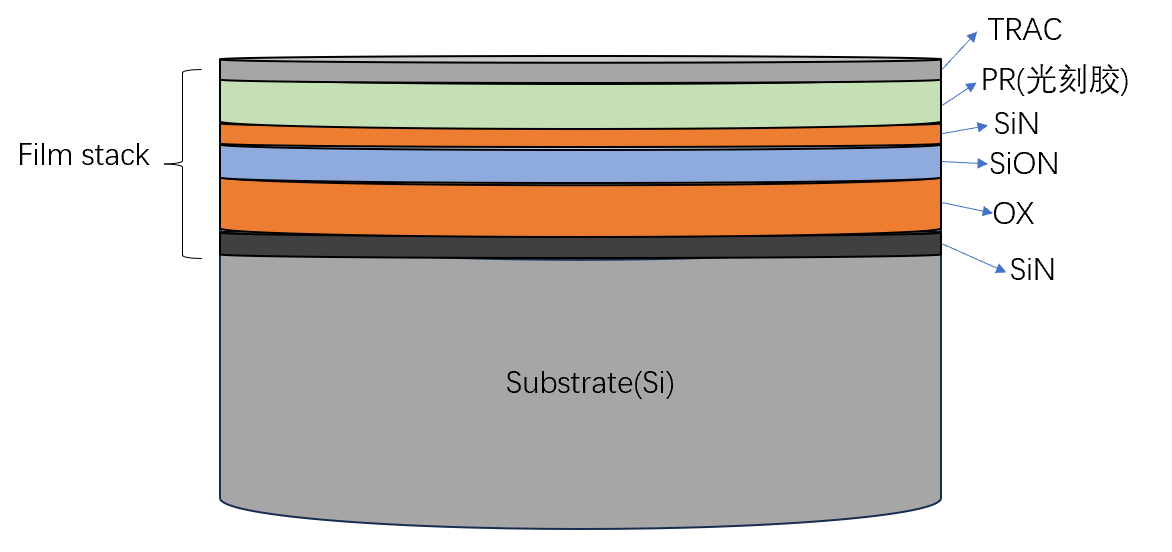

1.2 薄膜沉积

- 氧化层 / 介质层沉积:通过热氧化或化学气相沉积(CVD)在晶圆表面生成二氧化硅(SiO₂)等绝缘层。

- 金属层沉积:采用物理气相沉积(PVD)或电镀法形成铜、铝等金属互连层。

1.3 光刻工艺

- 光刻胶涂覆 :在晶圆表面旋涂光敏材料( 光刻胶)。

- 曝光与显影:通过掩膜版将电路图案投影到光刻胶上,显影后形成保护层。

1.4 刻蚀与掺杂

- 干法 / 湿法刻蚀:利用等离子体或化学试剂去除未被光刻胶保护的薄膜,形成电路结构。

- 离子注入:向特定区域掺入磷、硼等杂质,形成 N 型或 P 型半导体。

1.5 化学机械平坦化(CMP)

- 作用阶段:在每层金属或介质层沉积后,通过 CMP 去除表面多余材料(如铜、氧化硅),实现全局平坦化。

- 工艺目标:消除台阶效应,为下一层光刻提供平整基底,避免电路短路或信号干扰。

- CMP 主要应用于以下关键节点:

- 金属互连层平坦化

- 在铜或钨金属沉积后,通过 CMP 去除多余金属,仅保留沟槽内的布线结构,防止短路。

- 层间介质(ILD)平坦化

- 氧化硅等绝缘层沉积后,CMP 消除表面起伏,确保光刻精度。

- 多晶硅层处理

- 用于栅极结构平坦化,提升晶体管性能一致性。

- 金属互连层平坦化

1.6 多层互连重复

- 上述步骤(薄膜沉积→光刻→刻蚀→掺杂→CMP)循环进行,构建多层金属互连结构(通常 6 层以上)。

1.7 封装与测试

- 切割晶圆:将晶圆分割为单个芯片。

- 封装:通过引线键合、塑封等工艺保护芯片并连接外部引脚。

- 功能测试:验证芯片性能与可靠性。

二、Dummy 的作用

2.1 什么是 dummy

在芯片的空白区域(距离芯片设计图形 main pattern 大于 1um 左右开外),填充一些规整的矩形图形,不承担实际的任何芯片电路功能。虽不参与实际的功能运转,却对芯片这座假想的城市布局的稳定性至关重要。它由和芯片相同的材料构成,安静地 “待” 在芯片未被利用的空间里,不介入任何电路或逻辑运作。

为什么要加 dummy 呢?

芯片设计中,通常会出现 不均匀布局,这会导致芯片表面局部密度出现显著差异 。此外,为了提高良率, 在存储器或处理器中引入的冗余单元 (Redundancy Cells) 呈集中分布,这将进一步加剧芯片表面密度的波动。

在 CMP(化学机械平坦化)工艺过程中,需要做一些机械摩擦去除表面粗糙部位,对于表面材料分布不均匀的芯片,其不同区域因材料密度 (如金属、氧化物等) 的差异会导致抛光速率的不一致。低密度区域可能因过度抛光而出现凹陷(dishing),高密度区域可能因支撑不足而产生侵蚀(erosion)。这种抛光不均匀性会直接影响多层互连结构的平面度,进而引发短路或断路的问题。此外,金属线的侵蚀也会导致较为严重的 IR-Drop 以及信号线上的延迟。

为避免在图形平坦化过程中出现侵蚀和凹陷现象,需确保芯片整体密度的均匀性与一致性。通常的做法是在版图布线完成后,在标准单元间隙插入填充单元(如图 2 所示),填充单元是定义在标准单元库中且与电路逻辑无关的填充结构,即 Dummy。

dummy 常放在:

边缘区域:在晶圆的边缘,由于工艺限制和机械应力的影响,这里往往不是最佳的功能电路布局区域。放置 dummy 结构可以减少这些区域对内部有效电路的影响,并有助于均匀化蚀刻等工艺步骤。

切割道(scribe line, or street):划分各个芯片(die)的隐形边界,就像地图上的经纬线,为晶圆划片(dicing)提供精确引导,确保每个 die 被精准切割。

器件周围:为了提高制造工艺的一致性,特别是在晶体管或其他关键器件周围放置 dummy 图案。这有助于确保在进行化学机械抛光(CMP)、蚀刻等制程时,能有更均匀的结果,从而减少局部不规则性带来的影响。

空旷区域:如果某个区域没有功能性电路元件,可能会在这个区域内添加 dummy 结构。这样做不仅有助于平衡整个芯片表面的密度,还能帮助维持工艺步骤中如沉积、蚀刻等过程的稳定性。

特定功能区:在某些情况下,dummy 结构可能被用于特定的技术目的,例如改善电磁特性、热管理或者作为测试结构的一部分。

2.2 dummy 的作用

加固芯片 “防线”:Dummy 填充芯片空白区域,优化物理结构,增强晶圆边缘强度,有效减少划片和封装时芯片受损的可能,就像给脆弱的芯片边缘穿上了一层 “防护铠甲”。

工艺的 “稳定器”:晶圆边缘与中心区域电路密度不同,容易导致工艺不均匀。Dummy 通过模拟中心区域的电路布局,使整个晶圆的工艺保持均匀一致,确保每一处芯片制造工艺都 “整齐划一”。

制造过程的 “护航者”:光刻环节中,光线的反射与衍射容易引发曝光问题,导致蚀刻失败,影响关键元器件精度和尺寸。Dummy 能有效规避这些风险,保障制造顺利进行,让芯片制造的每一步都精准无误。

应力与翘曲的 “调节师”:芯片制造工艺易引发晶圆应力不均和翘曲,影响性能。Dummy 能够平衡应力分布,让晶圆保持平整,确保芯片性能稳定可靠。

信号的 “守护者”:在关键信号周围布置 Dummy 结构,能够有效阻挡杂波干扰,保证信号稳定传输,让芯片内部的 “信息高速公路” 畅通无阻。

性能测试的 “小助手”:芯片设计完成后,Dummy 可以协助测试功耗、速度、温度等性能指标,帮助工程师全方位了解芯片性能,为后续优化提供依据。

三、PTD 和 NTD 工艺

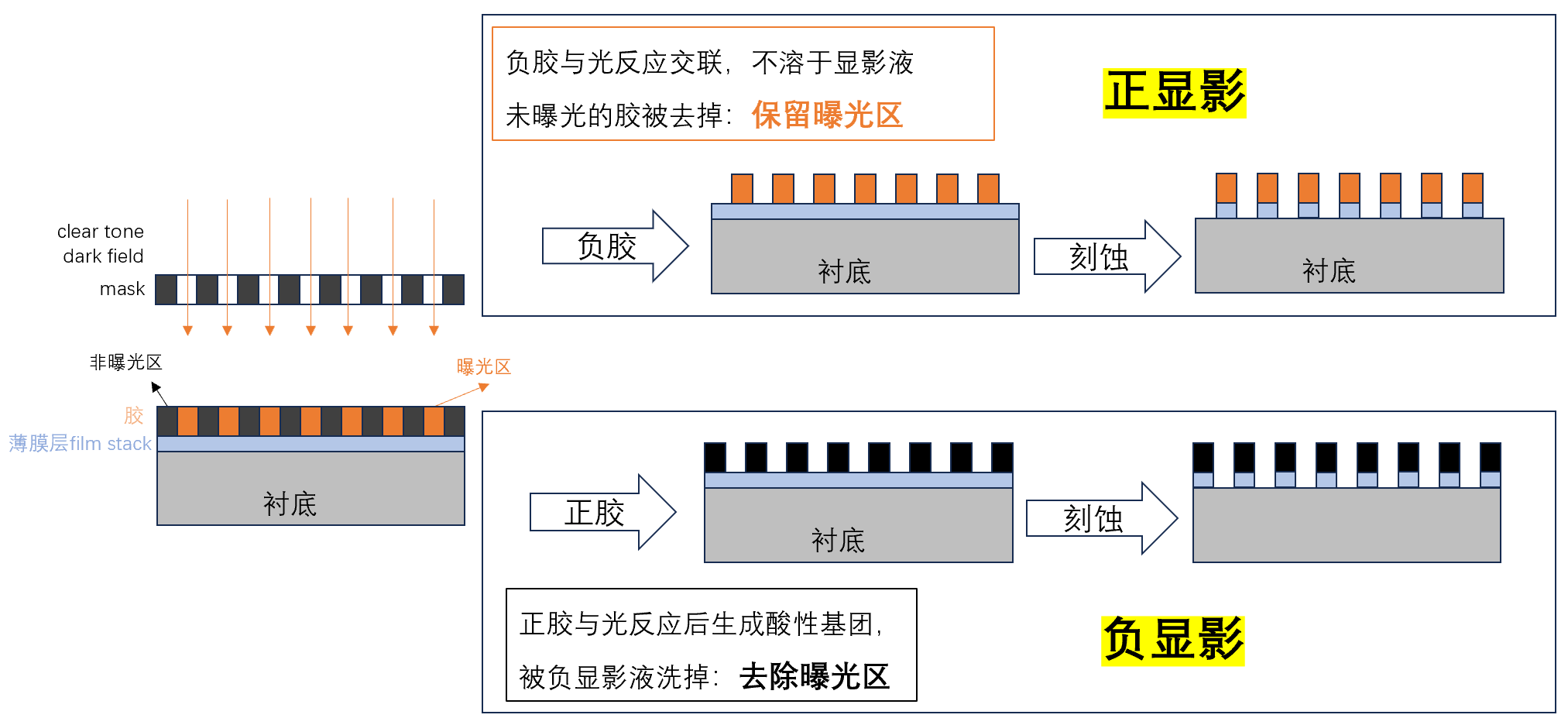

clear/dark tone: 指设计图形的透光性。

- clear tone 常用于线条,栅极,金属线图形

- dark tone 常用于接触孔,通孔,槽

clear/dark field mask:指掩模版的透光性。

3.1 PTD 正显影

正显影 ,即 Positive Tone Develop,简写 PTD。它是结合使用 负胶,搭配正显影液(如 TMAH 水溶液)来实现。

负胶(负光刻胶,负光阻, Negative Photoresist)暴露在光照下的区域会发生交联反应,变得更加难溶于显影液,最终保留在硅片表面,而未曝光区域则被冲洗掉。也就是说:PTD 工艺会保留曝光区

负胶由于分辨率不如正胶,更多应用在对线宽要求不极端苛刻的领域。用于 193nm 光刻的多数光刻胶是正性胶。

3.2 NTD 负显影

负显影 ,即 Negative Tone Develop,简写 NTD。它是结合使用 正胶,搭配负显影液(有机溶剂)来实现。

当正胶受到曝光时,光敏基团发生光化学反应,会生成酸性基团,放出氮气,酸性基团与显影液反应,光刻胶的结构被破坏,因此曝光后的光刻胶便被洗去。由于曝光后的光刻胶含有很多酸性基团,所以显影液一般为微碱性的溶液。

也就是说,NTD 工艺会去除曝光区,保留暗区

业内的 NTD 技术一般应用在 20nm 或 14nm 以下先进工艺节点量产中。

四、金属互联层

4.1 铜互联

在现代芯片制造中,金属层(尤其是铜互连)的制造普遍采用一种叫 大马士革(Damascene)工艺 的方法,因为铜的化学性质稳定,难以用干法刻蚀进行图形化。

- 先挖沟槽 (Trench):首先在绝缘介质层上,通过光刻和刻蚀工艺,刻出未来金属导线形状的 沟槽(Trench)和通孔(Via)。

- 再填充金属 (Metal):然后在这些沟槽里填充导电金属(如铜),填满整个沟槽。

- 最后抛光:通过化学机械抛光(CMP)将表面多余的金属磨掉,只留下沟槽里的金属。

工艺特点总结:

- 优点:铜的电阻率比铝低约 40%,能显著降低信号延迟(RC 延迟),提升芯片速度。其抗电迁移能力是铝的 10 倍以上,可靠性更高,能够承载更大的电流密度。

- 缺点:工艺流程复杂,步骤多,需要额外的阻挡层、种子层沉积设备和 CMP 设备,初始投资成本高。

4.2 铝互联

铝互连采用的是传统的“减法”工艺,其核心流程可以概括为:沉积 → 光刻 → 刻蚀。

工艺特点总结:

- 优点:工艺流程相对简单、成熟,设备成本较低。铝与下方的二氧化硅(SiO₂)绝缘层粘附性好。

- 缺点:当线宽缩小到纳米级别时,刻蚀工艺难以精确控制,容易产生缺陷。更重要的是,铝的电阻率较高,且抗电迁移能力差,在高电流密度下,铝原子会随电子流移动,导致导线断裂或短路,限制了芯片的性能和可靠性。

欢迎各位看官及技术大佬前来交流指导呀,可以邮件至 jqiange@yeah.net